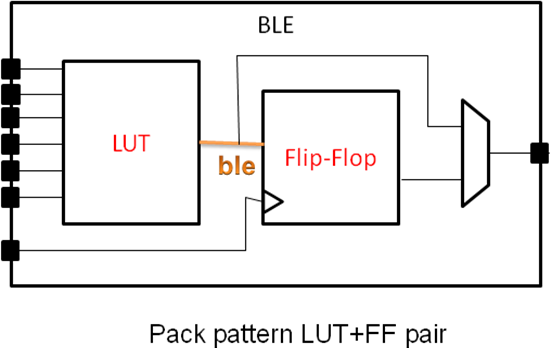

LUT with FlipFlop Example¶

An example of the classical LUT with FlipFlop pair shown in Figure 31 - Pack Pattern Example of the “Architecture Reference” section of the Verilog to Routing Documentation demonstrating the <pack_pattern> tag.

Fig. 31 - Pack Pattern Example

pair.sim.v¶

19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | `include "./lut4/lut4.sim.v"

`include "./dff/dff.sim.v"

`include "./omux/omux.sim.v"

module PAIR (

I,

CLK,

O

);

input wire [3:0] I;

input wire CLK;

output wire O;

(* pack="LUT2FF" *)

wire lut_out;

LUT4 lut (.I(I), .O(lut_out));

wire ff_out;

DFF dff (.CLK(CLK), .D(lut_out), .Q(ff_out));

parameter FF_BYPASS = "F";

OMUX #(.MODE(FF_BYPASS)) mux(.L(lut_out), .F(ff_out), .O(O));

endmodule

|

pair.model.xml¶

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 | <?xml version="1.0"?>

<models>

<model name="DFF">

<input_ports>

<port is_clock="1" name="CLK"/>

<port clock="CLK" name="D"/>

</input_ports>

<output_ports>

<port clock="CLK" name="Q"/>

</output_ports>

</model>

<model name="LUT4">

<input_ports>

<port combinational_sink_ports="O" name="I"/>

</input_ports>

<output_ports>

<port name="O"/>

</output_ports>

</model>

</models>

|

pair.pb_type.xml¶

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 | <?xml version="1.0"?>

<pb_type xmlns:xi="http://www.w3.org/2001/XInclude" name="PAIR" num_pb="1">

<clock name="CLK" num_pins="1"/>

<input name="I" num_pins="4"/>

<output name="O" num_pins="1"/>

<pb_type blif_model=".subckt DFF" name="dff" num_pb="1">

<clock name="CLK" num_pins="1"/>

<input name="D" num_pins="1"/>

<output name="Q" num_pins="1"/>

<T_setup clock="CLK" port="DFF.D" value="10e-12"/>

<T_hold clock="CLK" port="DFF.D" value="10e-12"/>

<T_clock_to_Q clock="CLK" max="10e-12" port="DFF.Q"/>

</pb_type>

<pb_type blif_model=".subckt LUT4" name="lut" num_pb="1">

<input name="I" num_pins="4"/>

<output name="O" num_pins="1"/>

<delay_matrix in_port="LUT4.I" out_port="LUT4.O" type="max">

30e-12 20e-12 11e-12 3e-12

</delay_matrix>

</pb_type>

<interconnect>

<mux input="dff.Q lut.O" name="mux" output="PAIR.O">

<metadata>

<meta name="fasm_mux">

dff.Q : mux.F

lut.O : mux.L

</meta>

<meta name="type">bel</meta>

<meta name="subtype">routing</meta>

</metadata>

</mux>

<direct input="PAIR.CLK" name="dff-CLK" output="dff.CLK"/>

<direct input="lut.O" name="dff-D" output="dff.D">

<pack_pattern in_port="lut.O" name="pack-LUT2FF" out_port="dff.D"/>

</direct>

<direct input="PAIR.I[0]" name="lut-I[0]" output="lut.I[0]"/>

<direct input="PAIR.I[1]" name="lut-I[1]" output="lut.I[1]"/>

<direct input="PAIR.I[2]" name="lut-I[2]" output="lut.I[2]"/>

<direct input="PAIR.I[3]" name="lut-I[3]" output="lut.I[3]"/>

</interconnect>

</pb_type>

|

Blackbox detection¶

Model of the leaf

pb_typeis generatedLeaf

pb_typeXML is generatedAll dependency models and

pb_types are included in the output files

Carry chain inference¶

pack_patterninference -pack_patterns defined on wires withpackattributes should be propagated topb_typeXMLs